芯片是我們這個時代最偉大的發明之一。如果沒有芯片的出現,我們很難想象當前的電子時代會是什么樣子。正是因為芯片的發明,所有的功能都集中在一個小芯片上。

一、芯片概念說明

芯片是集成電路的載體,它與晶片分開,通常是計算機或其他電子設備的重要組成部分。簡單地說,該芯片將我們隨處可見的電阻器和電容器等電子元件以及由它們組成的電路集成為一個小顆粒。芯片制造的過程就像用積木蓋房子一樣。首先,晶片作為基礎,通過層層堆疊,你可以完成你想要的形狀(即各種類型的芯片)。芯片是一種非常精密的儀器,其單位是納米。對于一個普通的英特爾酷睿CPU來說,核心部分的大小與人類指甲相似,但它集成了數十億甚至數百億個晶體管。芯片有很多種。一系列相互關聯的芯片可以組合成一個芯片組。它們相互依賴,結合在一起可以發揮更大的作用。例如,智能手機中的信號發送和接收模塊由多個芯片組成。更大的集成電路在一起。

芯片廣泛應用于我們的日常生活中,不同類型的芯片發揮著不同的作用。芯片就像人腦,接收信息,發出指令,控制人類行為。如果把CPU比作整個計算機系統的大腦,那么由CPU和其他芯片組成的芯片組就構成了整個身體的軀干。對于計算機來說,芯片組幾乎決定了整個系統的功能。不僅手機、電腦等智能產品含有芯片,可以說,只要涉及到一些更復雜的功能,它們就會被使用。

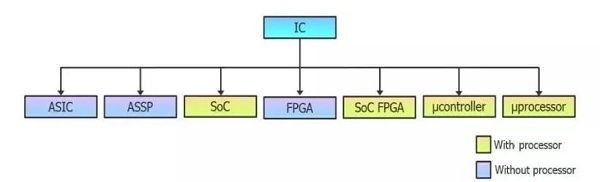

二、芯片的分類

下圖顯示了常見芯片的分類,包括ASIC、ASSP、SoC、FPGA、SoC FPGA、μ控制器、μ處理器等。

通用集成電路

ASIC(專用集成電路)是專門為特定應用或目的構建的集成電路。與可編程邏輯器件或標準邏輯集成電路相比,ASIC可以提高速度,因為它們是專門為完成一件事而設計的,并且可以做到這一點。它也可以做得更小,耗電更少。這種電路的缺點是設計和制造成本更高,尤其是在只需要幾個單元的情況下。

ASIC幾乎可以在任何電子設備中找到,其用途從自定義圖像渲染到聲音轉換。由于ASIC是定制的,它們只能由設計它們的公司使用,因此它們被視為專有技術。

ASSP:專用標準產品。專用標準產品(ASSP)的設計和實現與ASIC完全相同。這并不奇怪,因為它們本質上是一樣的。唯一的區別是ASSP是一種更通用的設備,適用于多個系統設計工作室。例如,獨立的USB接口芯片可以被歸類為ASSP。

SOC是片上系統的縮寫。由于它是一個系統,所以不能將單個系統稱為系統。只有多個個體的組合才能稱為系統。因此,SOC強調一個整體。SoC模仿了一個計算機系統,并被簡化為一個微系統。在我接觸過的SOC芯片中,硬件的大致組成部分是核心、存儲器、外圍接口(高速外圍設備和低速外圍設備)、總線、中斷模塊、時鐘模塊等。

現場可編程門陣列:現場可編程門陣列是一種半導體器件,由可編程互連連接的可配置邏輯塊矩陣組成。FPGA制造完成后,可以根據所需的應用或功能要求對其進行重新編程。這一特性是區分FPGA和專用集成電路(ASIC)的關鍵。您可以針對特定的設計任務定制FPGA設備。盡管市場上有一次性可編程(OTP)FPGA,但它們大多基于SRAM,并且可以隨著設計的發展而重新編程。

可編程SoC或SoC FPGA:集成處理器和FPGA架構的IC稱為可編程SoC或SoC FPGA。這還包括外圍設備、片上存儲器、FPGA式邏輯陣列和高速收發器。主要應用于網絡、航空航天、國防等領域。

微處理器(μP或MPU):只包含處理器的IC稱為微處理器。它不包含存儲器(RAM、ROM等)或任何其他外圍設備。

微控制器(μC或MCU):包含處理器、存儲器(RAM、ROM等)和其他外圍設備的IC稱為微控制器。這是一個通用設備,需要針對應用程序進行編程。微控制器可以用于各種工業產品中。微控制器是SoC的簡化版本。

三、芯片是如何設計和制造的?

芯片設計

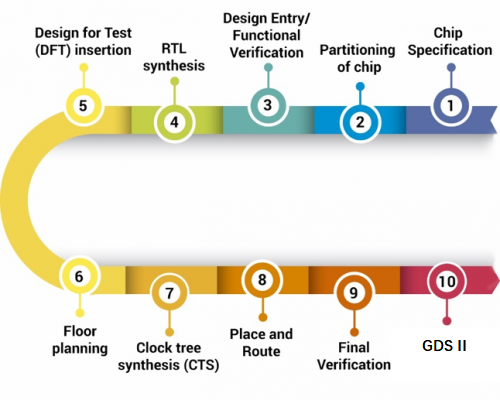

規范制定

在芯片設計公司內部,設計芯片的第一步是通過管理和數據分析起草提案,以便設計從一開始就滿足行業細分要求。此時,高層設計師將開會進行可行性分析,并在此基礎上確定芯片的功能和操作模式,確定性能、功能、物理尺寸、制造技術和設計技術等主要設計參數。

體系結構定義

定義系統的基本規范,例如浮點單位;確定要使用的系統,例如精簡指令集計算機(RISC)或復雜指令集計算機;最終確定ALU高速緩存大小的數量等。

特色設計

定義系統的主要功能單元,以幫助確定單元之間的互連要求,以及每個單元的物理和電氣規格。

邏輯設計

開發布爾表達式、控制流、字寬、寄存器分配等,并使用VHDL或Verilog HDL硬件描述語言在代碼中描述函數,形成寄存器傳輸級(RTL)代碼。

電路設計

邏輯設計給出了簡化的邏輯實現,而電路設計則以網表的形式進一步表達了邏輯。網表通常由柵極、晶體管和各種互連組成。電路設計的效果可以通過仿真得到。

物理設計

在這一步中,實現了網表到其幾何表示的轉換,結果被稱為布局,可以在功能上驗證合成的網表。此步驟遵循一些預定義的固定規則,例如lambda規則,該規則提供確切的細節,如組件大小、比例和間距。下一步是驗證已完成布線的物理布局的功能和時序。驗證項目通常包括LVS、DRC、ERC等,當然還有一些功耗分析和可制造性分析。

設計過程導出

這是芯片設計的最后一步。根據芯片代工廠的要求導出設計工藝文件。設計公司保留了原始設計草案,可以進行靈活的修改,而相對最終確定的工藝文件物理布局是基于GDS II文件。該格式被移交給芯片代工廠作為制造基礎。

制造和測試

精煉單晶硅錠

沙子是硅最便宜的來源,因此半導體材料中使用的硅是從沙子中提取的(二氧化硅?). 通常,生產單晶硅錠的公司從沙子中提取硅元素,然后經過高溫成型和多次純化,獲得純度為99.9999%的電子級硅(EGS)。然后在1400oC的鍋中熔化純硅,將含有所需晶體取向的小籽晶插入熔融的硅中,然后緩慢(1mm/min)拉出,使硅晶體制成圓柱形單晶硅錠。單個單晶硅錠的重量約為100kg。

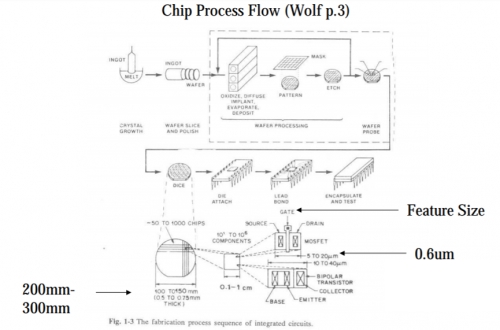

晶圓加工

晶圓加工主要包括兩個步驟。第一步是將單晶硅錠水平鋸成圓盤,然后拋光結晶,得到鏡面狀晶片。第二步是對晶片進行熱氧化。此時,純硅將通過充滿氧氣的高溫爐,在表面形成一層非常薄的二氧化硅,作為晶體管的柵極氧化層。

光刻

所謂的光刻工藝包括兩部分:掩模和光刻。首先,將具有光刻膠能力的光刻膠施加到晶片上,在硅襯底表面形成電路圖案,然后使用光對準器將晶片與掩模對準,晶片將穿過掩模的中空部分。當暴露在紫外光下時,光致抗蝕劑的暴露部分變得可溶,使得掩模上的電路結構被臨時復制到硅襯底上。

蝕刻

根據光刻機雕刻的電路結構,在硅片上進行微雕刻,雕刻凹槽或接觸孔。具體來說,蝕刻是將顯影后的光刻膠圖案作為掩模,然后使用化學液體或等離子體蝕刻掉襯底上一定深度的薄膜材料,然后獲得與光刻膠圖案相同的集成電路圖案。

離子注入

離子注入是芯片制造過程中的一項重要摻雜技術,也是控制MOSFET閾值電壓的重要手段。通常在真空和低溫環境中,磷化氫或三氯化硼的雜質離子被加速以獲得具有一定動能的雜質離子,然后將離子束拍攝到覆蓋有光刻膠掩模的晶片上。被光刻膠覆蓋的部分,離子束不能穿透光刻膠而被阻擋;在未被覆蓋的部分,離子束將被注入到襯底中以實現摻雜,而摻雜深度取決于離子束的能量。最后,在離子注入完成之后,在進行下一步驟之前,必須徹底去除光致抗蝕劑。

金屬化

金屬化是指通過沉積等方法在晶片上沉積金屬膜,然后通過金屬膜光刻形成表面金屬連接,將各種部件連接在一起的過程。因此,第一步是蝕刻接觸孔。第二步是制備金屬膜。主要導電金屬材料可以是鋁合金或金。方法通常包括蒸發、濺射、金屬CVD和電鍍。目前,金屬CVD具有很強的臺階覆蓋率和良好的高縱橫比。接觸和無間隙填充特性被廣泛使用。第三步是使用光刻和蝕刻工藝或剝離技術去除布線以外的部分,以形成互連的金屬線。第四步是進行合金化熱處理,以確保芯片和金屬之間具有良好的導電性。最后是平面化,減少了晶片表面不平整對光傳播精度的損害,從而影響了其精確的圖案制作。當金屬層增加時,該工藝不僅用于表層,也用于中間層。

晶片測試

在承載集成電路的晶片被處理之后,需要對其進行測試。主要目的是降低封裝成本,并盡早篩選出有問題的集成電路模塊(芯片原型)。具體操作是使用探針測試平臺,根據潔凈室中預先定義的測試點,測試芯片原型的電氣性能。該測試可以通過夾具對測試平臺上的晶片進行一次性測試,而不必逐個執行芯片,因此測試效率高。

切割和包裝

每個晶片包含數百到數萬個芯片。用金剛石鋸將晶片切割成單獨的片,進行薄化處理,然后對每個單獨的芯片(芯片)進行電氣測試。如果測試結果有問題,芯片將被丟棄;如果測試結果令人滿意,芯片將被送去封裝。在封裝之前,將使用顯微鏡對芯片進行重新檢查,只有通過重新檢查的芯片才會被真正封裝。

包裝測試

對于芯片,出廠前測試主要包括三個方面。前兩個是晶圓測試和芯片測試,在上一節中已經描述過(請參閱“切割和封裝”一章)。這里的重點實際上是第三個測試:封裝測試,即芯片出廠前的測試。據統計,這三項測試將占整個芯片生產成本的1/4至1/2。

此時,待測試的芯片已經被包裹在一層包裝中,并沒有那么脆弱。因此,對測試環境的要求沒有那么嚴格,也沒有必要進行潔凈室測試。然而,對于封裝測試,由于封裝本身的阻礙,測試探針無法接觸芯片內部,測試范圍有限,測試的復雜性也增加了。

通用芯片封裝測試包括多種電氣特性測試,如功耗、發熱、運行速度和各種環境下的耐受電壓。在測試過程中,經常需要大量的編程和編程驗證程序。有時,根據客戶的要求,會做一些有針對性的測試,看看客戶的需求是否得到滿足。當測試結果正常時,芯片將標有規格、型號和生產日期等絲網,并進行包裝和裝運。

四、總結

IC有很多種類型,每種類型的IC都有一定的特性:可編程或不可編程,有處理器或沒有處理器,高速或低速,緊湊或笨重。設計、制造和測試集成電路的過程是復雜而詳細的。主要貢獻者是設計和驗證團隊、IP供應商和IC制造商。先進的EDA工具在減少與IC設計周期相關的時間和精力方面發揮著至關重要的作用。

- 上一篇:什么是基帶處理器?

- 下一篇:2022年全球半導體行業十大技術趨勢